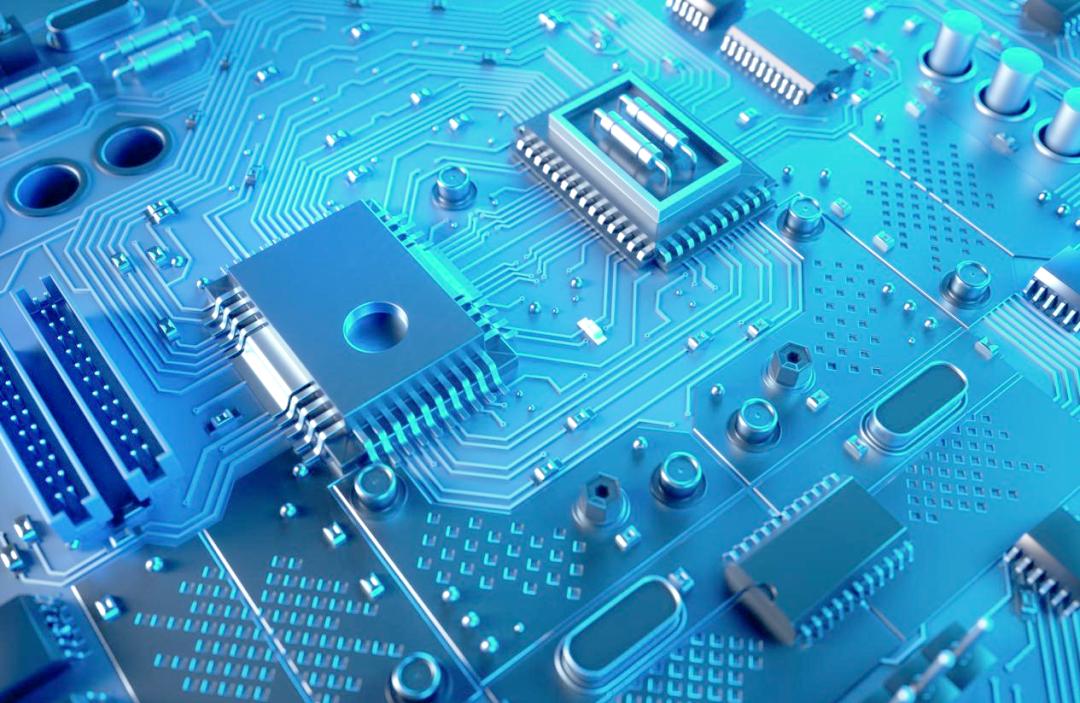

集成電路設計是現代電子工業的核心技術,涉及制造工藝、版圖設計和電參數設計規則三大關鍵領域。本文將詳細解析這三個方面的技術要點和發展趨勢。

一、集成電路制造工藝簡介

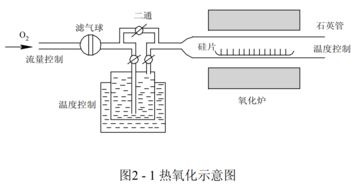

集成電路制造工藝是將設計好的電路圖轉化為實際芯片的關鍵過程,主要包括以下核心環節:

- 晶圓制備:以高純度硅為原料,通過拉晶、切片、拋光等工序制備晶圓基片

- 光刻技術:使用光刻機將設計圖形轉移到晶圓表面,是決定芯片特征尺寸的關鍵技術

- 刻蝕工藝:通過化學或物理方法去除不需要的材料,形成電路結構

- 摻雜工藝:通過離子注入或擴散技術改變半導體材料的電學特性

- 薄膜沉積:在晶圓表面沉積各種功能薄膜,包括金屬層、絕緣層等

- 化學機械拋光:實現表面平整化,為多層互連提供基礎

隨著技術發展,制造工藝已從微米級進入納米級,7nm、5nm等先進工藝成為主流。

二、版圖設計技術詳解

版圖設計是將邏輯電路轉化為物理布局的過程,主要包括:

- 布局規劃:確定芯片各功能模塊的位置和互連方式

- 單元設計:設計標準單元庫,包括邏輯門、存儲器等基本單元

- 自動布局布線:利用EDA工具自動完成元件布局和互連布線

- 物理驗證:通過DRC(設計規則檢查)、LVS(版圖與原理圖對比)等確保設計正確性

- 可靠性設計:考慮電遷移、天線效應等可靠性問題

現代版圖設計強調可制造性設計(DFM)和良率優化,需要在性能、面積和功耗之間取得平衡。

三、電參數設計規則概述

電參數設計規則確保芯片在特定工藝下滿足電氣性能要求,主要包括:

- 時序規則:建立時間、保持時間等時序約束條件

- 功耗規則:靜態功耗、動態功耗的約束和優化要求

- 信號完整性規則:串擾、噪聲容限等信號質量要求

- 電源完整性規則:電源噪聲、地彈等電源網絡要求

- 可靠性規則:電遷移、熱載流子效應等可靠性約束

這些規則通常以工藝設計工具包(PDK)的形式提供,設計師需要在設計過程中嚴格遵守。

四、技術發展趨勢

- 三維集成技術:通過TSV等技術實現芯片堆疊

- 異質集成:將不同工藝節點、不同材料的芯片集成

- AI輔助設計:利用人工智能技術優化設計流程

- 新型器件結構:FinFET、GAA等新型晶體管結構

集成電路設計是一個復雜的系統工程,需要制造工藝、版圖設計和電參數設計規則的緊密配合。隨著技術進步,這三個領域的協同創新將繼續推動集成電路產業向前發展。