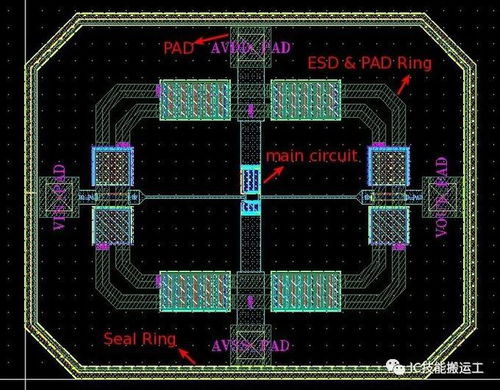

模擬集成電路設(shè)計(jì)是電子工程領(lǐng)域的關(guān)鍵環(huán)節(jié),涉及復(fù)雜的設(shè)計(jì)流程與多種電路模塊的協(xié)同工作。其中,ESD(靜電放電)保護(hù)電路和PAD(焊盤)電路作為集成電路與外部環(huán)境交互的重要接口,對(duì)芯片的可靠性和性能至關(guān)重要。本文將系統(tǒng)介紹模擬集成電路的設(shè)計(jì)流程,并重點(diǎn)分析ESD保護(hù)電路和PAD電路的設(shè)計(jì)原理、功能及其在整體設(shè)計(jì)中的應(yīng)用。

一、模擬集成電路設(shè)計(jì)流程概述

模擬集成電路設(shè)計(jì)通常遵循一個(gè)結(jié)構(gòu)化的流程,以確保芯片功能正確、性能穩(wěn)定且易于制造。主要步驟包括:

1. 規(guī)格定義:明確電路的功能需求、性能指標(biāo)(如增益、帶寬、功耗)和工作條件。

2. 架構(gòu)設(shè)計(jì):選擇合適的拓?fù)浣Y(jié)構(gòu),例如運(yùn)算放大器、比較器或電源管理電路。

3. 電路設(shè)計(jì):使用SPICE等工具進(jìn)行晶體管級(jí)設(shè)計(jì),優(yōu)化參數(shù)并滿足規(guī)格。

4. 仿真驗(yàn)證:通過直流、交流和瞬態(tài)仿真檢查電路行為,確保其在各種條件下可靠。

5. 版圖設(shè)計(jì):將電路轉(zhuǎn)換為物理布局,考慮匹配、寄生效應(yīng)和制造規(guī)則。

6. 后仿真:提取版圖寄生參數(shù)后重新仿真,驗(yàn)證性能是否達(dá)標(biāo)。

7. 測(cè)試與量產(chǎn):制造原型并進(jìn)行測(cè)試,最終投入批量生產(chǎn)。

在整個(gè)流程中,ESD保護(hù)電路和PAD電路的設(shè)計(jì)通常在版圖階段集成,但其規(guī)劃需從早期開始。

二、ESD保護(hù)電路的設(shè)計(jì)與作用

ESD保護(hù)電路是集成電路的“安全衛(wèi)士”,用于防止靜電放電對(duì)芯片造成永久性損壞。靜電可能來自人體、設(shè)備或環(huán)境,電壓可達(dá)數(shù)千伏,遠(yuǎn)超芯片耐受極限。ESD保護(hù)電路的主要功能是:

- 提供低阻抗路徑,將ESD電流引導(dǎo)至地或電源線。

- 限制內(nèi)部電路節(jié)點(diǎn)的電壓上升,避免晶體管擊穿。

- 快速響應(yīng)ESD事件(通常在納秒級(jí))。

常見ESD保護(hù)結(jié)構(gòu)包括:

- 二極管基結(jié)構(gòu):利用PN結(jié)的擊穿特性,將ESD電流分流。

- RC觸發(fā)SCR(硅控整流器):提供高電流處理能力,適用于高功耗應(yīng)用。

- 柵極接地NMOS(GGNMOS):在MOSFET中利用寄生雙極晶體管效應(yīng)進(jìn)行保護(hù)。

設(shè)計(jì)ESD保護(hù)電路時(shí),需平衡保護(hù)強(qiáng)度與性能影響,例如避免增加過多寄生電容而影響信號(hào)完整性。在模擬集成電路中,ESD電路常集成在PAD附近,并與電源鉗位電路協(xié)同工作。

三、PAD電路的設(shè)計(jì)與功能

PAD電路是芯片與外部世界的物理連接點(diǎn),負(fù)責(zé)信號(hào)、電源和地的輸入輸出。在模擬集成電路中,PAD設(shè)計(jì)需考慮電氣特性、可靠性和封裝兼容性。主要類型包括:

- 輸入PAD:接收外部信號(hào),通常包含ESD保護(hù)和高阻抗接口。

- 輸出PAD:驅(qū)動(dòng)外部負(fù)載,需提供足夠的電流和電壓擺幅。

- 電源PAD:分配電源和地,要求低電阻和抗噪聲能力。

PAD電路的設(shè)計(jì)要點(diǎn):

- 金屬層選擇:使用厚金屬以降低電阻和電感,提高電流承載能力。

- 尺寸優(yōu)化:根據(jù)封裝要求和電流密度確定PAD大小,避免過度占用芯片面積。

- 靜電防護(hù)集成:將ESD保護(hù)元件直接連接到PAD,確保快速響應(yīng)。

在模擬電路中,PAD可能還需包含緩沖器或電平移位器,以匹配內(nèi)部電路電壓水平。例如,在高速應(yīng)用中,PAD設(shè)計(jì)需最小化寄生電容和電感,以維持信號(hào)完整性。

四、ESD保護(hù)電路與PAD電路的協(xié)同設(shè)計(jì)

在模擬集成電路中,ESD保護(hù)電路和PAD電路需緊密集成,形成一個(gè)完整的I/O接口。設(shè)計(jì)時(shí)需遵循以下原則:

- 布局優(yōu)化:將ESD元件靠近PAD放置,縮短電流路徑,減少寄生效應(yīng)。

- 仿真驗(yàn)證:通過ESD仿真工具(如TLP測(cè)試)評(píng)估保護(hù)性能,確保滿足JEDEC等標(biāo)準(zhǔn)(如HBM模型要求≥2kV)。

- 可靠性考慮:在惡劣環(huán)境(如高溫)下測(cè)試電路穩(wěn)定性,避免漏電或失效。

實(shí)際案例中,例如在運(yùn)算放大器或數(shù)據(jù)轉(zhuǎn)換器中,ESD-PAD組合設(shè)計(jì)能顯著提高芯片的良率和壽命。

五、總結(jié)

模擬集成電路設(shè)計(jì)是一個(gè)多階段的過程,ESD保護(hù)電路和PAD電路作為關(guān)鍵接口模塊,直接影響芯片的可靠性和性能。通過系統(tǒng)化的設(shè)計(jì)流程、合理的ESD結(jié)構(gòu)選擇以及優(yōu)化的PAD布局,工程師可以確保芯片在真實(shí)環(huán)境中穩(wěn)定工作。未來,隨著工藝進(jìn)步和應(yīng)用需求多樣化,ESD和PAD設(shè)計(jì)將繼續(xù)演進(jìn),例如在低功耗和高速電路中探索新型保護(hù)方案。對(duì)于設(shè)計(jì)人員而言,掌握這些基礎(chǔ)模塊的原理與實(shí)踐,是成功實(shí)現(xiàn)高性能模擬集成電路的基石。