同步數字體系(SDH)是現代光通信網絡的核心技術之一,其開銷字節承載了豐富的管理與控制信息,對網絡的運行、管理與維護至關重要。為滿足高速、高可靠性的處理需求,設計一款專用的SDH開銷處理集成電路(ASIC)成為提升系統性能的關鍵。本文旨在探討SDH開銷處理專用集成電路的設計流程、核心模塊與實現要點。

一、設計背景與需求分析

SDH幀結構中的段開銷(SOH)和通道開銷(POH)包含了告警、性能監測、公務通信、數據通信通道(DCC)等重要信息。傳統的軟件或通用處理器處理方式在高速率(如STM-16及以上)場景下,往往面臨吞吐量不足和實時性差的挑戰。因此,專用集成電路的設計目標在于實現高速率(如2.5Gbps或更高)下的線速處理,具備低延遲、高可靠性、靈活可配置等特點,并能集成到更大的傳輸設備芯片中。

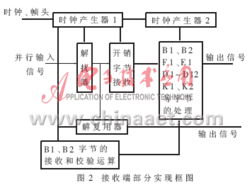

二、總體架構設計

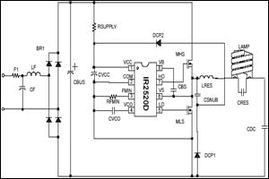

專用集成電路通常采用模塊化、流水線設計思想。總體架構可劃分為:

- 幀定位與同步模塊:負責從高速串行數據流中識別并鎖定SDH幀的起始位置,確保后續處理字節對齊。

- 開銷字節提取/插入模塊:根據配置,從特定時隙中提取開銷字節供處理,或將處理后的開銷字節插入回數據流。

- 核心處理引擎:這是設計的核心,通常包括:

- 告警檢測與產生單元:實時監測如LOS、LOF、AIS、RDI等告警信號。

- 性能監視單元:對B1、B2、B3等字節進行誤碼計算與統計。

- 開銷訪問與處理單元:對DCC(D1-D12)、公務字節(E1、E2)、使用者通道字節(F1)等進行讀寫與交換控制。

- 指針處理單元:對于VC-n級別的開銷,需處理AU/TU指針,完成同步與調整。

- 微處理器接口與控制寄存器組:提供與外部主控CPU(如ARM核)的接口(如APB、AHB總線),用于配置工作模式、查詢狀態、讀取性能數據等。

- 時鐘與復位管理模塊:產生內部各模塊所需的同步時鐘,并管理全局及局部復位。

三、關鍵技術與設計挑戰

- 高速數據接口設計:處理STM-N的高速串行數據流,需要精心設計串并轉換、時鐘數據恢復(CDR)電路,或與高速SerDes接口對接。

- 低延遲流水線:為確保處理不成為系統瓶頸,各功能模塊需高度流水化,精心平衡各級流水深度,優化關鍵路徑。

- 靈活可配置性:為適應不同網絡設備和應用場景,開銷處理的規則、映射路徑等應可通過軟件靈活配置,這增加了控制邏輯的復雜度。

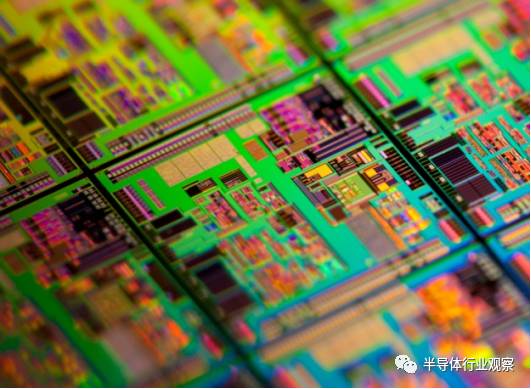

- 時序收斂與低功耗設計:在深亞微米工藝下,確保高速時鐘域下的時序收斂是一大挑戰。需采用時鐘門控、多電壓域等低功耗設計技術。

- 驗證的完備性:SDH協議復雜,開銷處理場景繁多,需要構建分層驗證環境,從模塊級到系統級,結合定向測試與隨機約束測試,確保功能百分百覆蓋協議要求。

四、設計流程與實現

遵循標準的數字集成電路設計流程:

- 使用硬件描述語言(如Verilog HDL)進行RTL級設計與編碼。

- 進行深入的功能仿真與驗證。

- 邏輯綜合,將RTL代碼映射到目標工藝庫的門級網表,進行時序約束與優化。

- 形式驗證,確保綜合前后邏輯功能一致性。

- 物理設計,包括布局規劃、時鐘樹綜合、布線、寄生參數提取、后仿真的物理驗證等。

- 流片與測試。

五、

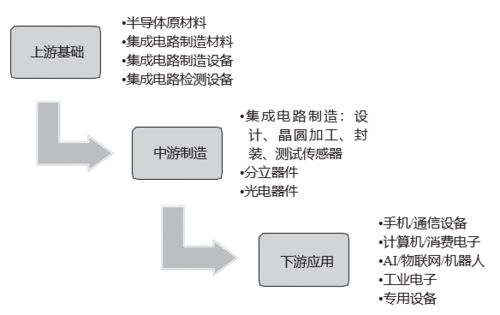

設計一款高性能的SDH開銷處理專用集成電路,是一項涉及通信協議深度理解與先進集成電路設計技術的綜合性工程。通過模塊化架構、流水線技術、以及嚴謹的設計驗證流程,可以實現滿足高速光通信設備要求的專用芯片。此類芯片的成功設計,不僅能提升傳輸設備的集成度與性能,還能降低系統的整體功耗與成本,是光通信核心器件自主化的重要一環。隨著網絡速率向更高速率演進和SDH與OTN等技術的融合,開銷處理ASIC的設計將面臨更大的帶寬、更靈活的處理能力以及更強的可編程性等新挑戰。